- 您现在的位置:买卖IC网 > Sheet目录3871 > PIC18F1230T-I/SO (Microchip Technology)IC PIC MCU FLASH 2KX16 18SOIC

PIC18F1230/1330

2009 Microchip Technology Inc.

DS39758D-page 241

MOVLW

Move Literal to W

Syntax:

MOVLW k

Operands:

0

k 255

Operation:

k

W

Status Affected:

None

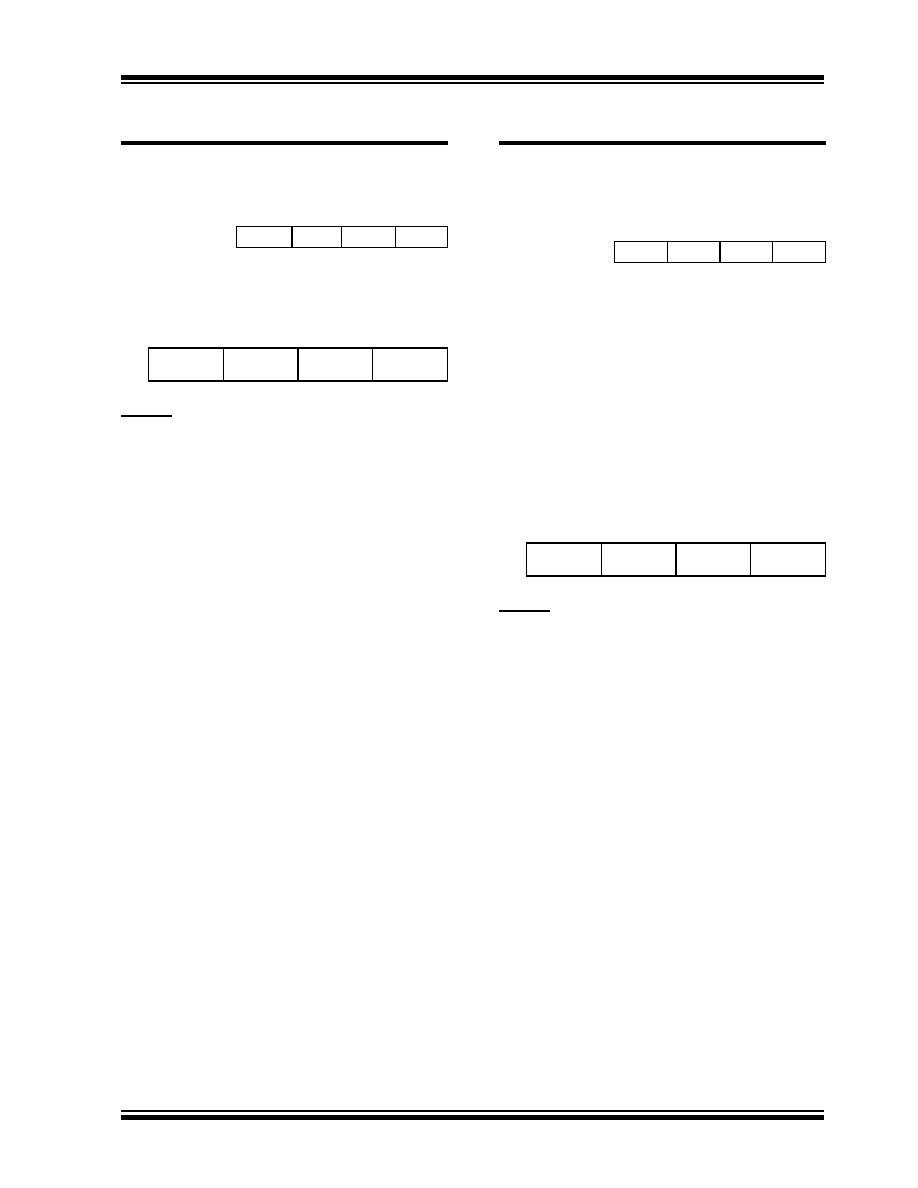

Encoding:

0000

1110

kkkk

Description:

The eight-bit literal ‘k’ is loaded into W.

Words:

1

Cycles:

1

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

literal ‘k’

Process

Data

Write to W

Example:

MOVLW

5Ah

After Instruction

W=

5Ah

MOVWF

Move W to f

Syntax:

MOVWF

f {,a}

Operands:

0

f 255

a

[0,1]

Operation:

(W)

f

Status Affected:

None

Encoding:

0110

111a

ffff

Description:

Move data from W to register ‘f’.

Location ‘f’ can be anywhere in the

256-byte bank.

If ‘a’ is ‘0’, the Access Bank is selected.

If ‘a’ is ‘1’, the BSR is used to select the

GPR bank.

If ‘a’ is ‘0’ and the extended instruction

set is enabled, this instruction operates

in Indexed Literal Offset Addressing

mode whenever f

95 (5Fh). See

for details.

Words:

1

Cycles:

1

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

register ‘f’

Process

Data

Write

register ‘f’

Example:

MOVWF

REG, 0

Before Instruction

W=

4Fh

REG

=

FFh

After Instruction

W=

4Fh

REG

=

4Fh

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F1330T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F65J50T-I/PT

IC PIC MCU FLASH 16KX16 64TQFP

PIC18F83J11T-I/PT

IC PIC MCU FLASH 4KX16 80TQFP

PIC16LF627-04/P

IC MCU FLASH 1KX14 COMP 18DIP

PIC18F86J55T-I/PT

IC PIC MCU FLASH 48KX16 80TQFP

PIC18F43K22-I/MV

MCU PIC 8KB FLASH 40QFN

PIC16C55A-04I/P

IC MCU OTP 512X12 28DIP

PIC18LF43K22-I/MV

MCU PIC 8KB FLASH 40UQFN

相关代理商/技术参数

PIC18F1230T-I/SS

功能描述:8位微控制器 -MCU 4KB Flash 256 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-E/ML

功能描述:8位微控制器 -MCU 8KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-E/P

功能描述:8位微控制器 -MCU 8KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-E/SO

功能描述:8位微控制器 -MCU 8KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-E/SS

功能描述:8位微控制器 -MCU 8KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-H/ML

功能描述:8位微控制器 -MCU 8KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-H/P

功能描述:8位微控制器 -MCU 8KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1320-H/SO

功能描述:8位微控制器 -MCU 8KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT